-

探索LIMS在綜合第三方平臺(tái)建設(shè)

-

高校實(shí)驗(yàn)室引入LIMS系統(tǒng)的優(yōu)勢(shì)

-

高校實(shí)驗(yàn)室中LIMS系統(tǒng)的應(yīng)用現(xiàn)狀

-

LIMS應(yīng)用在生物醫(yī)療領(lǐng)域的重要性

-

LIMS系統(tǒng)在醫(yī)藥行業(yè)的應(yīng)用

-

LIMS:實(shí)驗(yàn)室信息管理系統(tǒng)的模塊組成

-

如何選擇一款適合的LIMS?簡(jiǎn)單幾步助你輕松解決

-

LIMS:解決實(shí)驗(yàn)室管理的痛點(diǎn)

-

實(shí)驗(yàn)室是否需要采用LIMS軟件?

-

LIMS系統(tǒng)在化工化學(xué)行業(yè)的發(fā)展趨勢(shì)

武漢設(shè)計(jì)PCB制板廠家

PCB制板,即印刷電路板的制造,是現(xiàn)代電子技術(shù)不可或缺的重要環(huán)節(jié)。印刷電路板作為電子元器件的載體,不僅承擔(dān)著電路連接的基礎(chǔ)功能,還在電子設(shè)備的性能、穩(wěn)定性以及可靠性方面起著關(guān)鍵作用。隨著科技的進(jìn)步,PCB制板工藝也在不斷發(fā)展,逐漸朝著高密度、小型化和高精度的方向邁進(jìn)。在PCB制板的過(guò)程中,首先需要進(jìn)行電路設(shè)計(jì),利用專業(yè)的軟件將電路圖轉(zhuǎn)化為電路板的布局設(shè)計(jì)。這個(gè)階段涉及到元器件的合理布局,以減少信號(hào)干擾和提高電路性能。設(shè)計(jì)完成后,便進(jìn)入了制板的實(shí)際生產(chǎn)環(huán)節(jié)。制板工藝包括多次的圖形轉(zhuǎn)移、電鍍、蝕刻等過(guò)程,每一步都需要極其精細(xì)的操作,以確保電路的正確性與完整性。

半孔板工藝:0.5mm半孔金屬化,邊緣平滑無(wú)毛刺。武漢設(shè)計(jì)PCB制板廠家

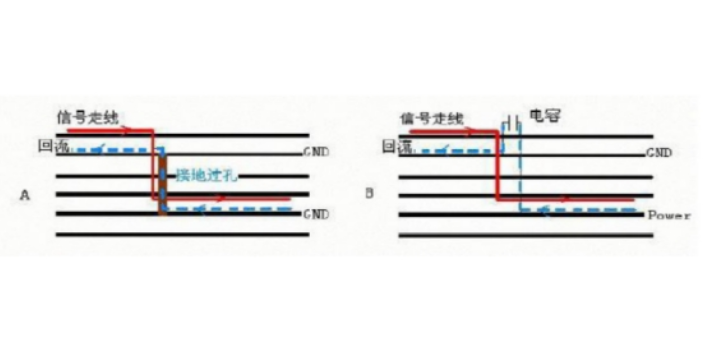

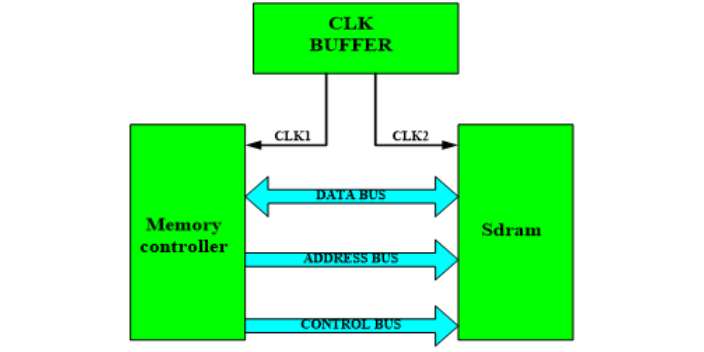

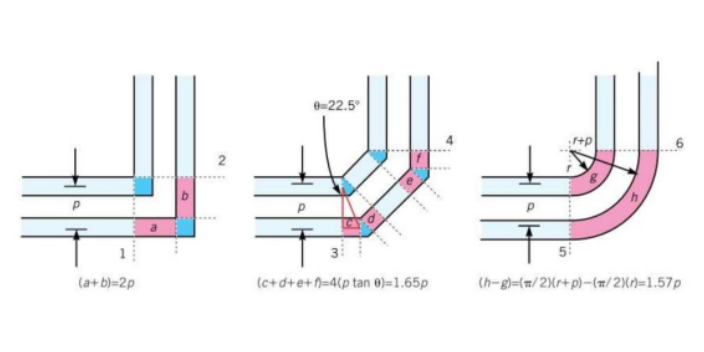

Inner_1),GND(Inner_2),Siganl_2(Bottom)。(3)POWER(Top),Siganl_1(Inner_1),GND(Inner_2),Siganl_2(Bottom)。顯然,方案3電源層和地層缺乏有效的耦合,不應(yīng)該被采用。那么方案1和方案2應(yīng)該如何進(jìn)行選擇呢?一般情況下,設(shè)計(jì)人員都會(huì)選擇方案1作為4層板的結(jié)構(gòu)。選擇的原因并非方案2不可被采用,而是一般的PCB板都只在頂層放置元器件,所以采用方案1較為妥當(dāng)。但是當(dāng)在頂層和底層都需要放置元器件,而且內(nèi)部電源層和地層之間的介質(zhì)厚度較大,耦合不佳時(shí),就需要考慮哪一層布置的信號(hào)線較少。對(duì)于方案1而言,底層的信號(hào)線較少,可以采用大面積的銅膜來(lái)與POWER層耦合;反之,如果元器件主要布置在底層,則應(yīng)該選用方案2來(lái)制板。如果采用如圖11-1所示的層疊結(jié)構(gòu),那么電源層和地線層本身就已經(jīng)耦合,考慮對(duì)稱性的要求,一般采用方案1。6層板在完成4層板的層疊結(jié)構(gòu)分析后,下面通過(guò)一個(gè)6層板組合方式的例子來(lái)說(shuō)明6層板層疊結(jié)構(gòu)的排列組合方式和方法。(1)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),Siganl_3(Inner_3),POWER(Inner_4),Siganl_4(Bottom)。方案1采用了4層信號(hào)層和2層內(nèi)部電源/接地層,具有較多的信號(hào)層。武漢了解PCB制板加工隨著智能科技的發(fā)展,對(duì)PCB制板的要求也越來(lái)越高。

PCB之所以能受到越來(lái)越廣泛的應(yīng)用,是因?yàn)樗泻芏嗒?dú)特的優(yōu)點(diǎn),大致如下: [2]可高密度化多年來(lái),印制板的高密度一直能夠隨著集成電路集成度的提高和安裝技術(shù)的進(jìn)步而相應(yīng)發(fā)展。 [2]高可靠性通過(guò)一系列檢查、測(cè)試和老化試驗(yàn)等技術(shù)手段,可以保證PCB長(zhǎng)期(使用期一般為20年)而可靠地工作。 [2]可設(shè)計(jì)性對(duì)PCB的各種性能(電氣、物理、化學(xué)、機(jī)械等)的要求,可以通過(guò)設(shè)計(jì)標(biāo)準(zhǔn)化、規(guī)范化等來(lái)實(shí)現(xiàn)。這樣設(shè)計(jì)時(shí)間短、效率高。 [2]可生產(chǎn)性PCB采用現(xiàn)代化管理,可實(shí)現(xiàn)標(biāo)準(zhǔn)化、規(guī)模(量)化、自動(dòng)化生產(chǎn),從而保證產(chǎn)品質(zhì)量的一致性。

PCB制板,即印刷電路板的制造,是現(xiàn)代電子技術(shù)不可或缺的重要環(huán)節(jié)。印刷電路板作為電子元器件的載體,不僅承擔(dān)著電路連接的基礎(chǔ)功能,還在電子設(shè)備的性能、穩(wěn)定性以及可靠性方面起著關(guān)鍵作用。隨著科技的進(jìn)步,PCB制板工藝也在不斷發(fā)展,逐漸朝著高密度、小型化和高精度的方向邁進(jìn)。在PCB制板的過(guò)程中,首先需要進(jìn)行電路設(shè)計(jì),利用專業(yè)的軟件將電路圖轉(zhuǎn)化為電路板的布局設(shè)計(jì)。這個(gè)階段涉及到元器件的合理布局,以減少信號(hào)干擾和提高電路性能。設(shè)計(jì)完成后,便進(jìn)入了制板的實(shí)際生產(chǎn)環(huán)節(jié)。制板工藝包括多次的圖形轉(zhuǎn)移、電鍍、蝕刻等過(guò)程,每一步都需要極其精細(xì)的操作,以確保電路的正確性與完整性。在這背后,技術(shù)人員和工程師們以嚴(yán)謹(jǐn)?shù)膽B(tài)度和豐富的經(jīng)驗(yàn),負(fù)責(zé)每一個(gè)環(huán)節(jié)的監(jiān)控與調(diào)整,從而確保**終產(chǎn)品的質(zhì)量。阻抗測(cè)試報(bào)告:每批次附TDR檢測(cè)數(shù)據(jù),透明化品控。

AltiumDesigner要求必須建立一個(gè)工程項(xiàng)目名稱。在原理圖SI分析中,系統(tǒng)將采用在SISetupOption對(duì)話框設(shè)置的傳輸線平均線長(zhǎng)和特征阻抗值;仿真器也將直接采用規(guī)則設(shè)置中信號(hào)完整性規(guī)則約束,如激勵(lì)源和供電網(wǎng)絡(luò)等,同時(shí),允許用戶直接在原理圖編輯環(huán)境下放置PCBLayout圖標(biāo),直接對(duì)原理圖內(nèi)網(wǎng)絡(luò)定義規(guī)則約束。當(dāng)建立了必要的仿真模型后,在原理圖編輯環(huán)境的菜單中選擇Tools->SignalIntegrity命令,運(yùn)行仿真。b.布線后(即PCB版圖設(shè)計(jì)階段)SI分析概述用戶如需對(duì)項(xiàng)目PCB版圖設(shè)計(jì)進(jìn)行SI仿真分析,AltiumDesigner要求必須在項(xiàng)目工程中建立相關(guān)的原理圖設(shè)計(jì)。此時(shí),當(dāng)用戶在任何一個(gè)原理圖文檔下運(yùn)行SI分析功能將與PCB版圖設(shè)計(jì)下允許SI分析功能得到相同的結(jié)果。當(dāng)建立了必要的仿真模型后,在PCB編輯環(huán)境的菜單中選擇Tools->SignalIntegrity命令,運(yùn)行仿真。4,操作實(shí)例:1)在AltiumDesigner的Protel設(shè)計(jì)環(huán)境下,選擇File\OpenProject,選擇安裝目錄下\Examples\ReferenceDesign\4PortSerialInterface\4PortSerial,進(jìn)入PCB編輯環(huán)境,如下圖1.圖1在PCB文件中進(jìn)行SI分析選擇Design/LayerStackManager…,配置好相應(yīng)的層后,選擇ImpedanceCalculation…。高頻板材定制:低損耗介質(zhì)材料,保障5G信號(hào)傳輸零延遲。武漢設(shè)計(jì)PCB制板廠家

線路設(shè)計(jì)與布局優(yōu)化:合理的線路設(shè)計(jì)和布局對(duì)于提高信號(hào)完整性和減少電磁干擾(EMI)至關(guān)重要。武漢設(shè)計(jì)PCB制板廠家

您既可以在原理圖又可以在PCB編輯器內(nèi)實(shí)現(xiàn)信號(hào)完整性分析,并且能以波形的方式在圖形界面下給出反射和串?dāng)_的分析結(jié)果。AltiumDesigner的信號(hào)完整性分析采用IC器件的IBIS模型,通過(guò)對(duì)版圖內(nèi)信號(hào)線路的阻抗計(jì)算,得到信號(hào)響應(yīng)和失真等仿真數(shù)據(jù)來(lái)檢查設(shè)計(jì)信號(hào)的可靠性。AltiumDesigner的信號(hào)完整性分析工具可以支持包括差分對(duì)信號(hào)在內(nèi)的高速電路信號(hào)完整性分析功能。AltiumDesigner仿真參數(shù)通過(guò)一個(gè)簡(jiǎn)單直觀的對(duì)話框進(jìn)行配置,通過(guò)使用集成的波形觀察儀,實(shí)現(xiàn)圖形顯示仿真結(jié)果,而且波形觀察儀可以同時(shí)顯示多個(gè)仿真數(shù)據(jù)圖像。并且可以直接在標(biāo)繪的波形上進(jìn)行測(cè)量,輸出結(jié)果數(shù)據(jù)還可供進(jìn)一步分析之用。AltiumDesigner提供的集成器件庫(kù)包含了大量的的器件IBIS模型,用戶可以對(duì)器件添加器件的IBIS模型,也可以從外部導(dǎo)入與器件相關(guān)聯(lián)的IBIS模型,選擇從器件廠商那里得到的IBIS模型。AltiumDesigner的SI功能包含了布線前(即原理圖設(shè)計(jì)階段)及布線后(PCB版圖設(shè)計(jì)階段)兩部分SI分析功能;采用成熟的傳輸線計(jì)算方法,以及I/O緩沖宏模型進(jìn)行仿真。基于快速反射和串?dāng)_模型,信號(hào)完整性分析器使用完全可靠的算法,從而能夠產(chǎn)生出準(zhǔn)確的仿真結(jié)果。武漢設(shè)計(jì)PCB制板廠家

- 荊門專業(yè)PCB制板 2025-05-04

- 鄂州印制PCB制板價(jià)格大全 2025-05-04

- 荊州專業(yè)PCB制板價(jià)格大全 2025-05-04

- 十堰正規(guī)PCB制板原理 2025-05-04

- 武漢定制PCB制板多少錢 2025-05-04

- 武漢定制PCB制板哪家好 2025-05-04

- 鄂州高速PCB制板原理 2025-05-04

- 咸寧焊接PCB制板功能 2025-05-04

- 鄂州打造PCB制板價(jià)格大全 2025-05-04

- 荊州印制PCB制板廠家 2025-05-04

- 徐州挑選晶舟轉(zhuǎn)換器直銷價(jià) 2025-05-04

- 嘉定區(qū)水平金屬橋架品牌哪家好 2025-05-04

- 什么價(jià)格池塘吸污機(jī)大概費(fèi)用 2025-05-04

- 吉林進(jìn)口智能監(jiān)控系統(tǒng)原料 2025-05-04

- 連云港防水LED會(huì)議室屏批發(fā) 2025-05-04

- 普陀區(qū)常規(guī)振動(dòng)篩設(shè)計(jì) 2025-05-04

- 寶山區(qū)制造薪酬管理服務(wù)特征 2025-05-04

- 重慶端吸緊耦合單機(jī)泵 2025-05-04

- 荊門專業(yè)PCB制板 2025-05-04

- 山東銀河直流熔斷器公司 2025-05-04