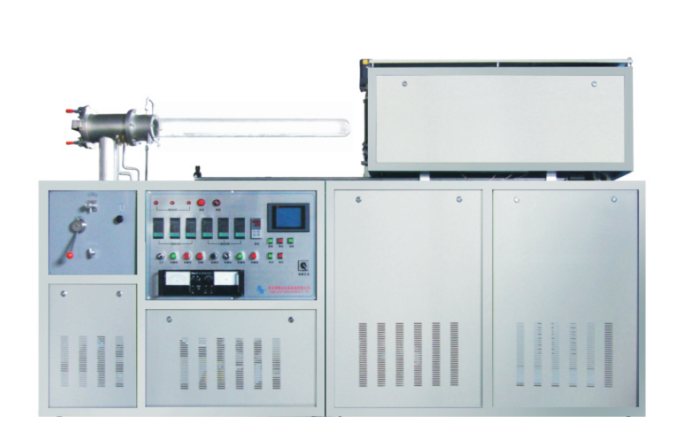

長沙制造管式爐生產廠家

管式爐在半導體熱氧化工藝中通過高溫環境下硅與氧化劑的化學反應生成二氧化硅(SiO?)薄膜,其關鍵機制分為干氧氧化(Si+O?→SiO?)、濕氧氧化(Si+H?O+O?→SiO?+H?)和水汽氧化(Si+H?O→SiO?+H?)三種模式。工藝溫度通常控制在 750℃-1200℃,其中干氧氧化因生成的氧化層結構致密、缺陷密度低,常用于柵極氧化層制備,需精確控制氧氣流量(50-500 sccm)和壓力(1-10 atm)以實現納米級厚度均勻性(±1%)。濕氧氧化通過引入水汽可將氧化速率提升 3-5 倍,適用于需要較厚氧化層(>1μm)的隔離結構,但需嚴格監測水汽純度以避免鈉離子污染。管式爐借熱輻射為半導體工藝供熱。長沙制造管式爐生產廠家

氧化工藝中管式爐的不可替代性:熱氧化是半導體器件制造的基礎步驟,管式爐在干氧/濕氧氧化中表現優異。干氧氧化(如1000°C下生成SiO?)生長速率慢但薄膜致密,適用于柵氧層;濕氧氧化(通入H?O蒸氣)速率快但多孔,常用于場氧隔離。管式爐的多段控溫可精確調節氧化層的厚度(±0.1 nm),而傳統批次式設計(50–100片/次)仍具成本優勢。近年來,部分產線采用快速氧化管式爐(RTO)以縮短周期,但高溫穩定性仍依賴傳統爐體結構。東北國產管式爐BCL3擴散爐管式爐通過先進控溫系統實現鋰電材料精確控溫。

管式爐用于半導體襯底處理時,對襯底表面的清潔度和單終止面的可控度有著重要影響。在一些研究中,改進管式爐中襯底處理工藝后,明顯提升了襯底表面單終止面的可控度與清潔度。例如在對鈦酸鍶(SrTiO?)、氧化鎂(MgO)等襯底進行處理時,通過精心調控管式爐的溫度、加熱時間以及通入的氣體種類和流量等參數,能夠有效去除襯底表面的污染物和氧化層,使襯底表面達到原子級別的清潔程度,同時精確控制單終止面的形成。高質量的襯底處理為后續在其上進行的半導體材料外延生長等工藝提供了良好的基礎,有助于生長出性能更優、缺陷更少的半導體結構,對于提升半導體器件的整體性能和穩定性意義重大。

管式爐在金屬硅化物(如TiSi?、CoSi?)形成中通過退火工藝促進金屬與硅的固相反應,典型溫度400℃-800℃,時間30-60分鐘,氣氛為氮氣或氬氣。以鈷硅化物為例,先在硅表面濺射50-100nm鈷膜,隨后在管式爐中進行兩步退火:第一步低溫(400℃)形成Co?Si,第二步高溫(700℃)轉化為低阻CoSi?,電阻率可降至15-20μΩ?cm。界面質量對硅化物性能至關重要。通過精確控制退火溫度和時間,可抑制有害副反應(如CoSi?向CoSi轉化),并通過預氧化硅表面(生長2-5nmSiO?)阻止金屬穿透。此外,采用快速熱退火(RTA)替代常規管式退火,可將退火時間縮短至10秒,明顯減少硅襯底中的自間隙原子擴散,降低漏電流風險。管式爐通過多層隔熱設計有效提升保溫效果。

擴散阻擋層用于防止金屬雜質(如Cu、Al)向硅基體擴散,典型材料包括氮化鈦(TiN)、氮化鉭(TaN)和碳化鎢(WC)。管式爐在阻擋層沉積中采用LPCVD或ALD(原子層沉積)技術,例如TiN的ALD工藝參數為溫度300℃,前驅體為四氯化鈦(TiCl?)和氨氣(NH?),沉積速率0.1-0.2nm/循環,可精確控制厚度至1-5nm。阻擋層的性能驗證包括:①擴散測試(在800℃下退火1小時,檢測金屬穿透深度<5nm);②附著力測試(劃格法>4B);③電學測試(電阻率<200μΩ?cm)。對于先進節點(<28nm),采用多層復合阻擋層(如TaN/TiN)可將阻擋能力提升3倍以上,同時降低接觸電阻。賽瑞達管式爐助力半導體材料表面改性,效果出眾,速詢詳情!西安8吋管式爐銷售

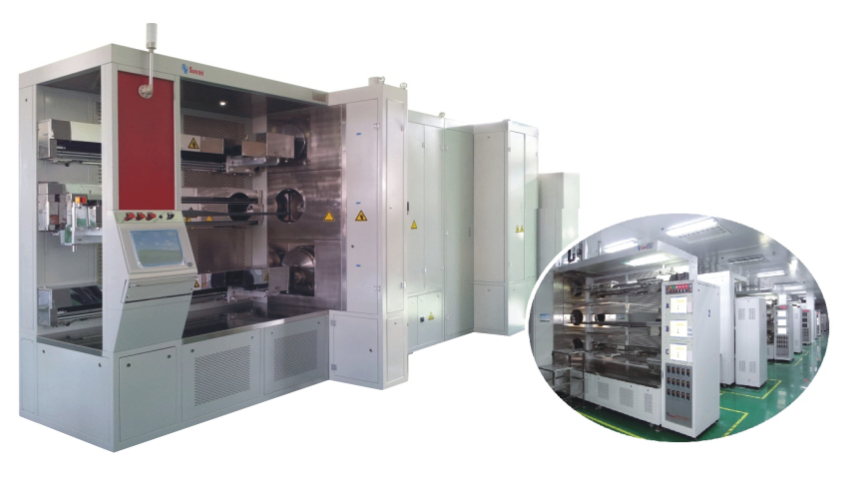

管式爐的自動化系統提升半導體工藝效率。長沙制造管式爐生產廠家

管式爐在氧化擴散、薄膜沉積等關鍵工藝中,需要實現納米級精度的溫度控制。通過采用新型的溫度控制算法和更先進的溫度傳感器,管式爐能夠將溫度精度提升至 ±0.1℃甚至更高,從而確保在這些先進工藝中,半導體材料的性能能夠得到精確控制,避免因溫度波動導致的器件性能偏差。此外,在一些先進的半導體制造工藝中,還對升溫降溫速率有著嚴格要求,管式爐通過優化加熱和冷卻系統,能夠實現快速的升溫降溫,提高生產效率的同時,滿足先進工藝對溫度變化曲線的特殊需求,為先進半導體工藝的發展提供了可靠的設備保障。長沙制造管式爐生產廠家

- 安徽6吋管式爐 2025-07-14

- 北京智能管式爐化學氣相沉積CVD設備TEOS工藝 2025-07-14

- 上海制造管式爐銷售 2025-07-14

- 成都制造管式爐SIPOS工藝 2025-07-14

- 珠三角賽瑞達管式爐生產廠家 2025-07-14

- 重慶一體化管式爐SiN工藝 2025-07-14

- 深圳8英寸管式爐氧化爐 2025-07-14

- 成都賽瑞達管式爐氧化退火爐 2025-07-14

- 杭州第三代半導體管式爐摻雜POLY工藝 2025-07-14

- 山東8英寸管式爐真空退火爐 2025-07-14

- 巢湖信息系統集成服務哪個好 2025-07-14

- 四川方形風扇報價 2025-07-14

- 高精度視覺檢測有幾種 2025-07-14

- 浙江國產失重式喂料機維修 2025-07-14

- 合肥紅沖沖床供應廠家 2025-07-14

- 江西板式智能加工中心門板生產線技術指導 2025-07-14

- 靜安區中藥壓片機定制價格 2025-07-14

- 江蘇碳鋼井蓋蓋板施工安裝 2025-07-14

- 天津制造物聯網應用服務 2025-07-14

- 煙臺等離子切割機報價 2025-07-14