-

十堰印制PCB制板原理

十堰印制PCB制板原理PCB行業(yè)進(jìn)入壁壘PCB進(jìn)入壁壘主要包括資金壁壘、技術(shù)壁壘、客戶認(rèn)可壁壘、環(huán)境壁壘、行業(yè)認(rèn)證壁壘、企業(yè)管理壁壘等。1客源壁壘:PCB對電子信息產(chǎn)品的性能和壽命至關(guān)重要。為了保證質(zhì)量,大客戶一般采取嚴(yán)格的“合格供應(yīng)商認(rèn)證制度”,并設(shè)定6-24個月的檢驗周期。只有...

2023-09-24 -

武漢高速PCB培訓(xùn)銷售電話

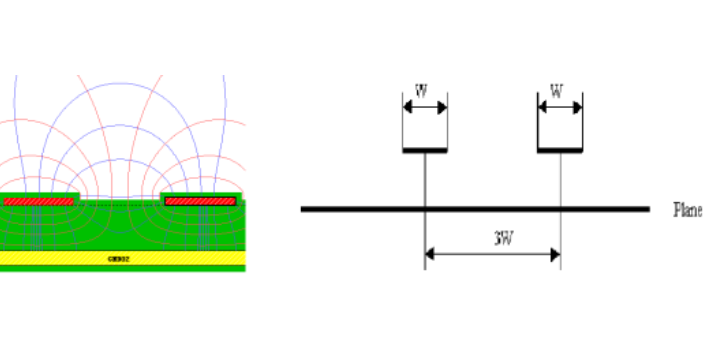

武漢高速PCB培訓(xùn)銷售電話折疊布線1、導(dǎo)線⑴寬度印制導(dǎo)線的最小寬度,主要由導(dǎo)線和絕緣基板間的粘附強(qiáng)度和流過它們的電流值決定。印制導(dǎo)線可盡量寬一些,尤其是電源線和地線,在板面允許的條件下盡量寬一些,即使面積緊張的條件下一般不小于1mm。特別是地線,即使局部不允許加寬,也應(yīng)在允許的地方加寬...

2023-09-24 -

隨州定制PCB制板多少錢

隨州定制PCB制板多少錢PCB制板層壓設(shè)計在設(shè)計多層PCB電路板之前,設(shè)計師需要首先根據(jù)電路規(guī)模、電路板尺寸和電磁兼容性(EMC)要求確定電路板結(jié)構(gòu),即決定使用四層、六層還是更多層電路板。確定層數(shù)后,確定內(nèi)部電氣層的位置以及如何在這些層上分配不同的信號。這是多層PCB層壓結(jié)構(gòu)的選擇。...

2023-09-23 -

黃岡正規(guī)PCB制版哪家好

黃岡正規(guī)PCB制版哪家好在PCB出現(xiàn)之前,電路是通過點到點的接線組成的。這種方法的可靠性很低,因為隨著電路的老化,線路的破裂會導(dǎo)致線路節(jié)點的斷路或者短路。繞線技術(shù)是電路技術(shù)的一個重大進(jìn)步,這種方法通過將小口徑線材繞在連接點的柱子上,提升了線路的耐久性以及可更換性。當(dāng)電子行業(yè)從真空管、...

2023-09-23 -

湖北什么是PCB培訓(xùn)批發(fā)

湖北什么是PCB培訓(xùn)批發(fā)電壓河水之所以能夠流動,是因為有水位差;電荷之所以能夠流動,是因為有電位差。電位差也就是電壓。電壓是形成電流的原因。在電路中,電壓常用U表示。電壓的單位是伏(V),也常用毫伏(mV)或者微伏(uV)做單位。1V=1000mV,1mV=1000uV。電壓可以用電...

2023-09-23 -

荊門打造PCB制版哪家好

荊門打造PCB制版哪家好根據(jù)制造材料的不同,PCB分為剛性板、柔性板、剛性-柔性板和封裝基板。剛性板按層數(shù)分為單板、雙板、多層板。多層板按制造工藝不同可分為普通多層板、背板、高速多層板、金屬基板、厚銅板、高頻微波板、HDI板。封裝基板由HDI板發(fā)展而來,具有高密度、高精度、高性能、小...

2023-09-23 -

荊州焊接PCB制版銷售

荊州焊接PCB制版銷售PCB制版在各種電子設(shè)備中的作用1.焊盤:為固定和組裝集成電路等各種電子元件提供機(jī)械支撐。2.布線:實現(xiàn)集成電路等各種電子元器件之間的布線和電氣連接(信號傳輸)或電氣絕緣。提供所需的電氣特性,如特性阻抗。3.綠油絲印:為自動組裝提供阻焊圖形,為元件插入、檢查和...

2023-09-22 -

宜昌專業(yè)PCB制版哪家好

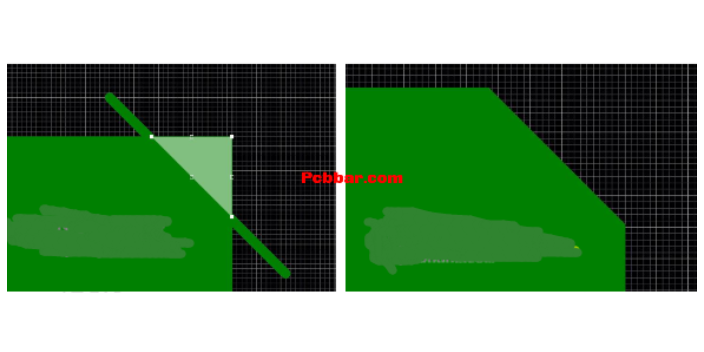

宜昌專業(yè)PCB制版哪家好Cadence中X-net的添加 1.打開PCB文件: (1).首先X-net是添加在串阻和串容上的一個模型,使得做等長的時候電阻或電容兩邊的網(wǎng)絡(luò)變成一個網(wǎng)絡(luò),添加方法如下: 1):找到串阻或者串容 2):在Analyze->Mod...

2023-09-22 -

黃石設(shè)計PCB制版哪家好

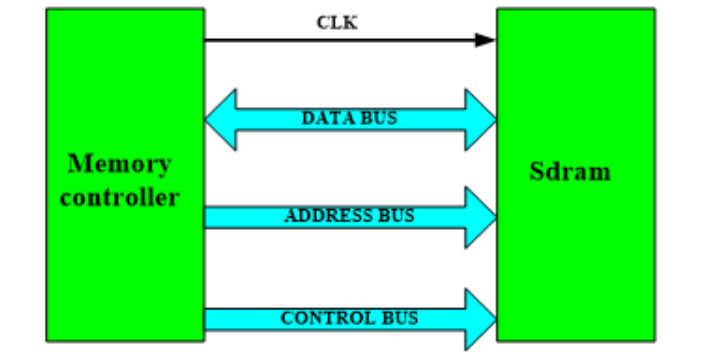

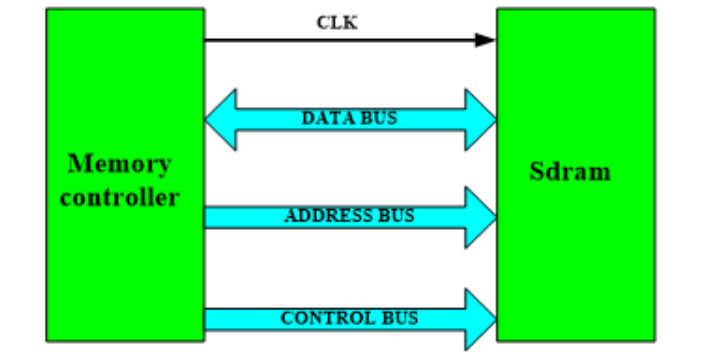

黃石設(shè)計PCB制版哪家好SDRAM各管腳功能說明: 1、CLK是由系統(tǒng)時鐘驅(qū)動的,SDRAM所有的輸入信號都是在CLK的上升沿采樣,CLK還用于觸發(fā)內(nèi)部計數(shù)器和輸出寄存器; 2、CKE為時鐘使能信號,高電平時時鐘有效,低電平時時鐘無效,CKE為低電平時SDRAM處于預(yù)...

2023-09-22 -

荊州定制PCB制板價格大全

荊州定制PCB制板價格大全PCB的扇孔在PCB設(shè)計中,過孔的扇出是很重要的一環(huán),扇孔的方式會影響到信號完整性、平面完整性、布線的難度,以至于增加生產(chǎn)成本。從扇孔的直觀目的來講,主要是兩個。1.縮短回流路徑,縮短信號的回路、電源的回路2.打孔占位,預(yù)先打孔占位可以防止不打孔情況下走線太密...

2023-09-21 -

黃岡印制PCB制板包括哪些

黃岡印制PCB制板包括哪些PCB制板基本存在于電子設(shè)備中,又稱印刷電路板。這種由貴金屬制成的綠色電路板連接設(shè)備的所有電氣元件,使其正常運行。沒有PCB,電子設(shè)備就無法工作。PCB制板是簡單的二維電路設(shè)計,顯示不同元件的功能和連接。所以PCB原理圖是印刷電路板設(shè)計的一部分。這是一種圖形表...

2023-09-21 -

鄂州印制PCB制板銷售電話

鄂州印制PCB制板銷售電話SDRAM各管腳功能說明:1、CLK是由系統(tǒng)時鐘驅(qū)動的,SDRAM所有的輸入信號都是在CLK的上升沿采樣,CLK還用于觸發(fā)內(nèi)部計數(shù)器和輸出寄存器;2、CKE為時鐘使能信號,高電平時時鐘有效,低電平時時鐘無效,CKE為低電平時SDRAM處于預(yù)充電斷電模式和自刷新...

2023-09-21 -

武漢哪里的PCB設(shè)計

武漢哪里的PCB設(shè)計生成Gerber文件(1)生成Gerber文件:根據(jù)各EDA軟件操作,生成Gerber文件。(2)檢查Gerber文件:檢查Gerber文件步驟:種類→數(shù)量→格式→時間。Gerber文件種類及數(shù)量:各層線路、絲印層、阻焊層、鋼網(wǎng)層、鉆孔表、IPC網(wǎng)表必須齊全且...

2023-09-21 -

孝感專業(yè)PCB設(shè)計規(guī)范

孝感專業(yè)PCB設(shè)計規(guī)范電源電路放置優(yōu)先處理開關(guān)電源模塊布局,并按器件資料要求設(shè)計。RLC放置(1)濾波電容放置濾波電容靠近管腳擺放(BGA、SOP、QFP等封裝的濾波電容放置),多與BGA電源或地的兩個管腳共用同一過孔。BGA封裝下放置濾波電容:BGA封裝過孔密集很難把所有濾波電容...

2023-09-21 -

荊州哪里的PCB設(shè)計布局

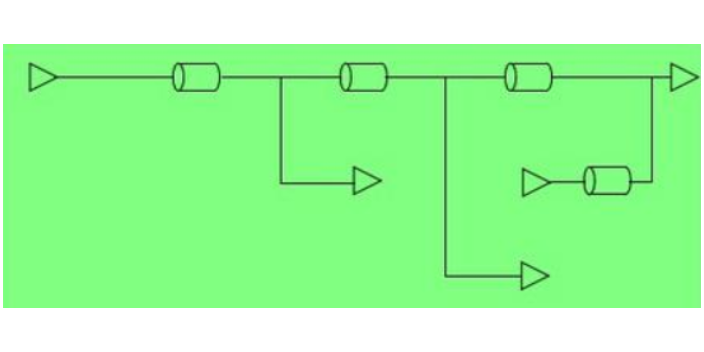

荊州哪里的PCB設(shè)計布局DDR的PCB布局、布線要求4、對于DDR的地址及控制信號,如果掛兩片DDR顆粒時拓?fù)浣ㄗh采用對稱的Y型結(jié)構(gòu),分支端靠近信號的接收端,串聯(lián)電阻靠近驅(qū)動端放置(5mm以內(nèi)),并聯(lián)電阻靠近接收端放置(5mm以內(nèi)),布局布線要保證所有地址、控制信號拓?fù)浣Y(jié)構(gòu)的一致性及...

2023-09-14 -

黃岡了解PCB設(shè)計銷售

黃岡了解PCB設(shè)計銷售印制電路板的設(shè)計是以電路原理圖為根據(jù),實現(xiàn)電路設(shè)計者所需要的功能。印刷電路板的設(shè)計主要指版圖設(shè)計,需要考慮外部接口、內(nèi)部的電磁保護(hù)、散熱等因素布局。我們常用的設(shè)計軟件有AltiumDesigner、CadenceAllegro、PADS等等設(shè)計軟件。在高速設(shè)計...

2023-09-14 -

荊州打造PCB設(shè)計加工

荊州打造PCB設(shè)計加工工藝方面注意事項(1)質(zhì)量較大、體積較大的SMD器件不要兩面放置;(2)質(zhì)量較大的元器件放在板的中心;(3)可調(diào)元器件的布局要方便調(diào)試(如跳線、可變電容、電位器等);(4)電解電容、鉭電容極性方向不超過2個;(5)SMD器件原點應(yīng)在器件中心,布局過程中如發(fā)現(xiàn)異...

2023-05-15 -

黃岡正規(guī)PCB設(shè)計廠家

黃岡正規(guī)PCB設(shè)計廠家評估平面層數(shù),電源平面數(shù)的評估:分析單板電源總數(shù)與分布情況,優(yōu)先關(guān)注分布范圍大,及電流大于1A以上的電源(如:+5V,+3.3V此類整板電源、FPGA/DSP的核電源、DDR電源等)。通常情況下:如果板內(nèi)無BGA封裝的芯片,一般可以用一個電源層處理所有的電源;...

2023-05-15 -

黃石定制PCB設(shè)計教程

黃石定制PCB設(shè)計教程關(guān)鍵信號布線(1)射頻信號:優(yōu)先在器件面走線并進(jìn)行包地、打孔處理,線寬8Mil以上且滿足阻抗要求,如下圖所示。不相關(guān)的線不允許穿射頻區(qū)域。SMA頭部分與其它部分做隔離單點接地。(2)中頻、低頻信號:優(yōu)先與器件走在同一面并進(jìn)行包地處理,線寬≥8Mil,如下圖所示...

2023-05-15 -

襄陽正規(guī)PCB設(shè)計廠家

襄陽正規(guī)PCB設(shè)計廠家SDRAM的端接1、時鐘采用∏型(RCR)濾波,∏型濾波的布局要緊湊,布線時不要形成Stub。2、控制總線、地址總線采用在源端串接電阻或者直連。3、數(shù)據(jù)線有兩種端接方法,一種是在CPU和SDRAM中間串接電阻,另一種是分別在CPU和SDRAM兩端串接電阻,具體...

2023-05-15 -

黃岡如何PCB設(shè)計走線

黃岡如何PCB設(shè)計走線ADC/DAC電路:(4)隔離處理:隔離腔體應(yīng)做開窗處理、方便焊接屏蔽殼,在屏蔽腔體上設(shè)計兩排開窗過孔屏蔽,過孔應(yīng)相互錯開,同排過孔間距為150Mil。,在腔體的拐角處應(yīng)設(shè)計3mm的金屬化固定孔,保證其固定屏蔽殼,隔離腔體內(nèi)的器件與屏蔽殼的間距>0.5mm。如...

2023-05-15 -

十堰PCB設(shè)計銷售

十堰PCB設(shè)計銷售繪制各禁止布局、布線、限高、亮銅、挖空、銑切、開槽、厚度削邊區(qū)域大小,形狀與結(jié)構(gòu)圖完全一致,所在層由各EDA軟件確定。對以上相應(yīng)區(qū)域設(shè)置如下特性:禁布區(qū)設(shè)置禁止布局、禁止布線屬性;限高區(qū)域設(shè)置對應(yīng)高度限制屬性;亮銅區(qū)域鋪相應(yīng)網(wǎng)絡(luò)屬性銅皮和加SolderMask...

2023-05-15 -

荊門什么是PCB設(shè)計加工

荊門什么是PCB設(shè)計加工1VGA接口(1)VGA接口介紹VGA(VideoGraphicsArray)接口是顯卡上輸出模擬信號的接口,VGA接口是顯卡上應(yīng)用為大范圍的接口類型,雖然液晶顯示器可以直接接收數(shù)字信號,但為了與VGA接口顯卡相匹配,也采用了VGA接口。一般VGA模擬信號在超...

2023-05-15 -

宜昌正規(guī)PCB設(shè)計包括哪些

宜昌正規(guī)PCB設(shè)計包括哪些生成Gerber文件(1)生成Gerber文件:根據(jù)各EDA軟件操作,生成Gerber文件。(2)檢查Gerber文件:檢查Gerber文件步驟:種類→數(shù)量→格式→時間。Gerber文件種類及數(shù)量:各層線路、絲印層、阻焊層、鋼網(wǎng)層、鉆孔表、IPC網(wǎng)表必須齊全且...

2023-05-15 -

十堰打造PCB設(shè)計怎么樣

十堰打造PCB設(shè)計怎么樣SDRAM時鐘源同步和外同步1、源同步:是指時鐘與數(shù)據(jù)同時在兩個芯片之間間傳輸,不需要外部時鐘源來給SDRAM提供時鐘,CLK由SDRAM控制芯片(如CPU)輸出,數(shù)據(jù)總線、地址總線、控制總線信號由CLK來觸發(fā)和鎖存,CLK必須與數(shù)據(jù)總線、地址總線、控制總線信...

2023-03-11 -

襄陽高效PCB設(shè)計價格大全

襄陽高效PCB設(shè)計價格大全DDR模塊,DDRSDRAM全稱為DoubleDataRateSDRAM,中文名為“雙倍數(shù)據(jù)率SDRAM”,是在SDRAM的基礎(chǔ)上改進(jìn)而來,人們習(xí)慣稱為DDR,DDR本質(zhì)上不需要提高時鐘頻率就能加倍提高SDRAM的數(shù)據(jù)傳輸速率,它允許在時鐘的上升沿和下降沿讀...

2023-03-11 -

宜昌高速PCB設(shè)計怎么樣

宜昌高速PCB設(shè)計怎么樣ADC/DAC電路:(2)模擬地與數(shù)字地處理:大多數(shù)ADC、DAC往往依據(jù)數(shù)據(jù)手冊和提供的參考設(shè)計進(jìn)行地分割處理,通常情況是將PCB地層分為模擬地AGND和數(shù)字地DGND,然后將二者單點連接,(3)模擬電源和數(shù)字電源當(dāng)電源入口只有統(tǒng)一的數(shù)字地和數(shù)字電源時,在電...

2023-03-11 -

宜昌打造PCB設(shè)計規(guī)范

宜昌打造PCB設(shè)計規(guī)范SDRAM模塊SDRAM介紹:SDRAM是SynchronousDynamicRandomAccessMemory(同步動態(tài)隨機(jī)存儲器)的簡稱,是使用很的一種存儲器,一般應(yīng)用在200MHz以下,常用在33MHz、90MHz、100MHz、125MHz、133M...

2023-03-11 -

孝感高速PCB設(shè)計批發(fā)

孝感高速PCB設(shè)計批發(fā)布線優(yōu)化布線優(yōu)化的步驟:連通性檢查→DRC檢查→STUB殘端走線及過孔檢查→跨分割走線檢查→走線串?dāng)_檢查→殘銅率檢查→走線角度檢查。(1)連通性檢查:整板連通性為100%,未連接網(wǎng)絡(luò)需確認(rèn)并記錄《項目設(shè)計溝通記錄》中。(2)整板DRC檢查:對整板DRC進(jìn)行檢查...

2023-03-11 -

什么是PCB設(shè)計價格大全

什么是PCB設(shè)計價格大全存儲模塊介紹:存儲器分類在我們的設(shè)計用到的存儲器有SRAM、DRAM、EEPROM、Flash等,其中DDR系列用的是多的,其DDR-DDR4的詳細(xì)參數(shù)如下:DDR采用TSSOP封裝技術(shù),而DDR2和DDR3內(nèi)存均采用FBGA封裝技術(shù)。TSSOP封裝的外形尺寸...

2023-03-11